*[Mano의 컴퓨터 시스템 구조 3판]의 공부할겸 요약한 내용입니다.

개요

CPU

1) 컴퓨터에서 데이터 처리 동작을 수행하는 부분을 중앙 처리 장치(CPU)라고 한다.

2) CPU는 세 부분으로 구성된다.

레지스터 집합(Register Set)

1) 명령어를 실행하는데 필요한 중간 데이터를 보관

산술 논리 장치(ALU)

1) 명령어를 실행하기 위한 마이크로 연산을 수행

제어 장치(Control Unit: CU)

1) 레지스터 사이의 정보 전송을 감시하거나 ALU에서 수행할 동작을 지시

스택 구조

1) 대다수의 컴퓨터의 CPU가 가지고 있는 매우 활용도 높은 기법

2) 스택 또는 Last-In,First-Out(LIFO)라고 한다.

3) 가장 나중에 메모리에 저장되는 내용이 가장 먼저 꺼내지도록 하는 저장 장치

스택 포인터(SP)

1) 스택은 근본적으로 단지 수를 세는 역할만 하는 주소 레지스터를 가진 메모리

2) 이런 주소 레지스터를 스택 포인터라고 한다.

3) 이것의 값은 항상 스택의 꼭대기 주소를 가리키고 있다.

스택의 두가지 동작

PUSH: 메모리에 항목을 넣는 동작

POP: 빼내는 동작

레지스터 스택

1) 제한된 수의 메모리 워드나 레지스터들로 구성

2) 상대적으로 빠른 처리 속도

PUSH

SP <- SP+1: SP 증가시킨다.M[SP] <- DR: 스택의 top에 항목을 적는다.if (SP=0) then (FULL <- 1): 스택이 full임을 확인한다.EMTY <- 0: 스택이 empty가 아님을 표시한다.

POP

DR <- M[SP]: 스택으로부터 항목을 읽는다.SP <- SP-1: SP를 하나 감소시킨다.if (SP=0) then (EMTY <- 1): 스택이 empty임을 확인한다.FULL <- 0: 스택이 full이 아님을 표시한다.

메모리 스택

1) CPU에 부착시킨 RAM 메모리를 이용하여 구현

2) 상대적으로 많은 정보 저장

3) 스택의 상한과 하한을 저장하는 두개의 레지스터를 이용해서 스택의 한계를 검사할 수 있다.

4) PUSH 동작 후에는 SP와 상한 레지스터를 비교하고 POP 동작 후에는 SP와 하한 레지스터 비교

PUSH

SP <- SP-1: SP 감소시킨다.

M[SP] <- DR: 스택의 top에 항목을 적는다.

POP

DR <- M[SP]: 스택으로부터 항목을 읽는다.

SP <- SP+1: SP를 하나 감소시킨다.

역 Polish 표기(Postfix)

A+B: infix 개념, 사람이 사용하는 기법

+AB: prefix 또는 polish 개념, 컴파일러에서 사용하는 기법

AB+: postfix 또는 역(reverse) polish 개념, 스택에서 사용하는 기법

명령어 형식

명령어 코드의 비트는 필드(field)라고 불리는 몇 개의 그룹으로 나뉜다.

1. 수행해야 할 연산을 명시한 연산 코드 필드

2. 메모리의 주소나 레지스터를 지정하는 주소 필드

3. 피연산자나 유효 주소가 결정되는 방법을 나타내는 모드 필드

주소 필드의 개수에 따른 분류

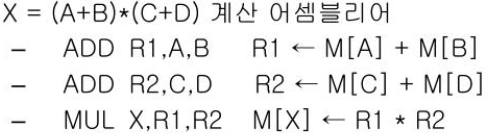

3-주소 명령어

1) 각 주소 필드가 레지스터를 지정할 수 있고 메모리의 주소를 지정할 수 있다.

2) 프로그램 길이가 짧지만 명령어의 길이가 길다는 단점이 있다.

2-주소 명령어

1) 실제 사용되는 컴퓨터에서 가장 흔히 사용되는 방식이다.

2) 3-주소 명령어보다 명령어가 짧아진 대신 프로그램의 길이가 길어진다.

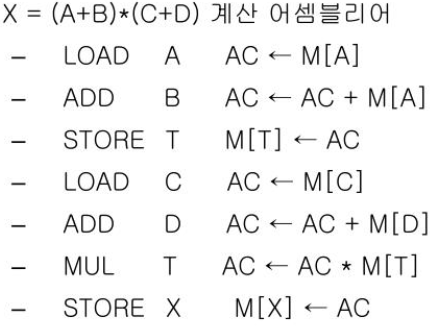

1-주소 명령어

1) 2-주소 명령어보다 명령어가 짧은 대신 프로그램의 길이가 길어진다.

무주소 명령어

RISC 명령

1) RISC 프로세서의 명령어 집합은 메모리와 CPU 사이의 통신을 할 때 LOAD와 STORE명령어만 사용하도록 제한된다.

2) LOAD 명령어를 이용하여 메모리부터 피연산자 CPU 레지스터로 읽어온다.

3) 계산 결과를 STORE 명령어로 메모리에 저장하는 절차

어드레싱 모드(Addressing Modes)

1) 실제의 피연산자를 정하기 위해 명령어 속에 있는 주소 필드의 값을 수정하거나 다른 것으로 대체하는 것들을 규정

2) 포인터, 카운터 인덱싱, 프로그램 리로케이션 등의 편의를 사용자에게 제공함으로써 융통성을 줌

3) 명령어의 주서 필드의 비트를 줄인다.

다양한 어드레싱 모드

1) implied 모드

2) immediate 모드

3) 레지스터 모드

4) 레지스터 간접 모드

5) 자동증가 또는 자동감소 모드

6) 직접 주소 모드

7) 간접 주소 모드

8) 상대 주소 모드

9) 인덱스드 어드레싱 모드

10) 베이스 레지스터 어드레싱 모드

프로그램 제어

서브루틴 Call과 Return

서브루틴

1) 어떤 특정한 작업을 수행하도록 자체가 일련의 명령어들로 구성되어 있는 프로그램

2) 모든 서브루틴의 마지막 명령어는 return from subroutine인데, 이는 기억해둔 리턴 주소를 프로그램에 넣는 것이다.

3) 기종에 따라 레지스터, 특정 위치의 메모리, 서브루틴의 첫 번째 위치, 스택 등을 사용한다.

4) 가장 효율적인 것은 스택이다.

Call

SP <- SP+1: 스택 포인터를 하나 증가시킨다.M[SP] <- PC: PC의 내용을 스택에 놓는다.PC <- 유효 주소: 서브루틴으로 프로그램이 수행되게 한다.

Return

PC <- M[SP]: 스택의 top의 값을 PC에 넣는다.SP <- SP-1: SP를 하나 감소시킨다.

프로그램 인터럽트

정상적인 프로그램의 진행을 벗어나게 하는 여러가지 문제들을 다루는 것이다.

세 가지 형태의 인터럽트

외부 인터럽트 - CPU의 H/W 신호에 의해 발생

1) 입출력 장치, 타이밍 장치, 전원 등 외부적인 요인으로 발생하는 것

2) 입출력 장치가 데이터의 전송을 요구하거나, 정보 전송이 끝났음을 알릴 때, 정해진 시간이 지났을 때, 전원 공급이 끊어질 때

내부 인터럽트 - CPU의 H/W 신호에 의해 발생

1) 불법적인 명령어나 데이터를 사용할 때 발생하는 것

2) 오버플로가 발생했거나, 0으로 나눈다거나, 스택이 넘치거나, 메모리 보호가 어려워졌을 때 발생된다.

스프트웨어 인터럽트

1) 명령어의 수행에 의해 일어난다.

2) 가장 흔한 소프트웨어 인터럽트로는 감독자 call 명령어의 사용이다.

CISC vs RISC

ClSC(Complex Instruction Set Computing)의 주된 특징

1) 많은 수의 명령어 - 일반적으로 100에서 250개의 명령어

2) 몇몇 명령어는 특별한 동작을 수행하여 자주 사용되지 않는다.

3) 다양한 어드레싱 모드 - 일반적으로 5에서 20가지의 모드

4) 가변 길이 명령어 형식

5) 메모리의 피연산자를 처리하는 명령어

6) 마이크로 프로그램된 제어 사용

RISC(Reduced Intruction Set Computing)의 주된 특징

1) 상대적으로 적은 수의 명령어2) 상대적으로 적은 수의 어드레싱 모드3) 메모리 참조는 load와 store 명령어에서만으로 제한 된다.4) 모든 동작은 CPU의 레지스터 안에서 수행된다.5) 고정된 길이의 명령어 형식으로 디코딩이 간단하다.6) 단일 사이크르이 명령어 실행7) 마이크로 프로그램된 제어보다는 하드와이어된 제어를 채택8) 속도가 빠르다. 상대적으로 고가이다. 특수 목적에 사용된다.9) 레지스터의 수가 더 많다.

'컴퓨터 구조' 카테고리의 다른 글

| [컴퓨터 구조] 메모리 구조 (0) | 2022.06.11 |

|---|---|

| [컴퓨터 구조] 마이크로 프로그램을 이용한 제어 장치 (0) | 2022.05.21 |

| [컴퓨터 구조] 명령어 구조 및 실행 과정과 Hardwired 제어 장치 (0) | 2022.05.11 |

| [컴퓨터 구조] 마이크로 연산 (0) | 2022.05.05 |

| [컴퓨터 구조] Register 전송 (0) | 2022.05.04 |