*[Mano의 컴퓨터 시스템 구조 3판]의 공부할겸 요약한 내용입니다.

마이크로 연산은 레지스터에 저장된 데이터에 대해 수행되는 기본적인 연산으로 디지털 컴퓨터에서 흔히 사용되는 마이크로 연산은 다음과 같다.

1) 레지스테 사이에서 이진 정보를 전송하는 레지스터 전송 마이크로 연산

2) 레지스터에 저장된 수치 데이터에 대해 산술 연산을 수행하는 산술 마이크로 연산

3) 레지스터에 저장된 비수치 데이터에 대해 비트 조작 연산을 수행하는 논리 마이크로 연산

4) 레지스터에 저장된 데이터에 대해 시프트 연산을 수행하는 시프트 마이크로 연산

1. 산술 마이크로 연산

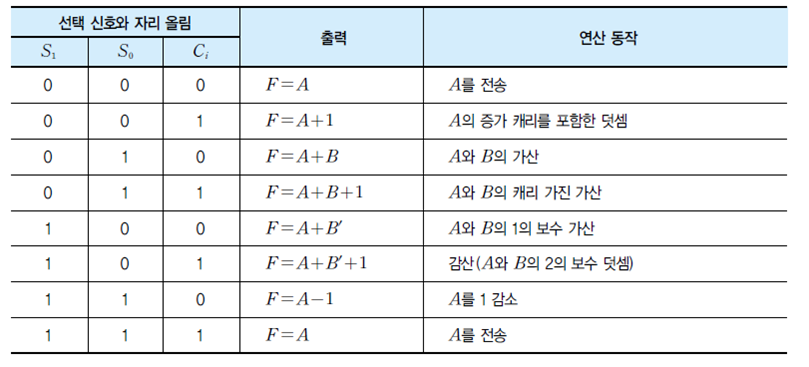

산술 마이크로 연산은 다음과 같은 문장으로 정의된다.

R3 <- R1 + R2

레지스터 R1과 R2 내용의 합을 R3로 전송하는 이 문장을 구현하기 위해서는 세개의 레지스터와 덧셈 연산을 위한 하드웨어가 필요하다.

뺄셈 연산은 보통 보수와 덧셈을 이용한다.

R3 <- R1 - R2 = R1 + (R2'+1) *R2의 2의 보수

이진 가산기

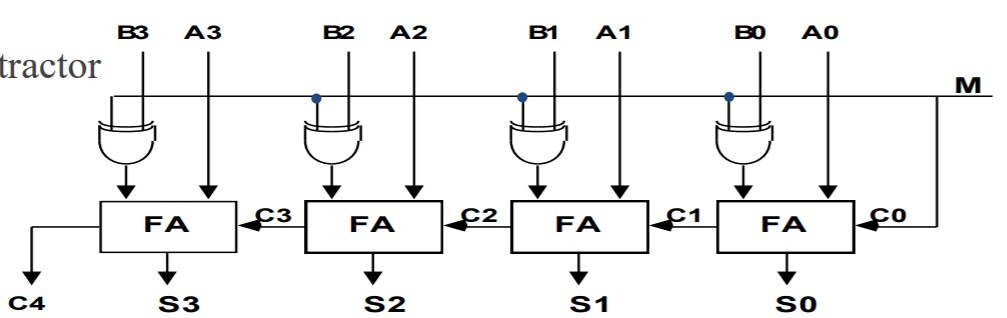

1) 임의의 길이를 가진 두 이진수에 대한 덧셈을 수행하는 회롤를 이진 가산기라고 한다.

2) 여러개의 전가산기들을 직렬로 연결하여 이전 것의 캐리 출력이 다음 것의 캐리로 입력 되도록 구성한다.

3) 피가수 A와 가수 B의 각 비트들은 오른쪽에서 왼쪽으로 나열되어있다.

4) 캐리들은 전가산기들을 통해 사슬로 연결되어 있다.

5) C0와 C4는 입력과 출력 캐리를 나타내며, S 출력은 합에 대한 각 비트를 나타낸다.

6) 부호도 숫자와 같이 처리하며, 음수는 2의 보수로 입력한다.

*몫 = S3 S2 S1 S0, 여기서 맨 왼쪽 FA는 부호, C4는 버림

이진 가감산기

1) 각 전가산기에 XOR게이트를 추가하면 덧셈과 뺄셈 연산은 하나의 동일한 회로로 구현될 수 있다.

2) M이 0이면 가산기(+)로 동작하고 M이 1이면 감산기(-)로 동작한다.

3) M = 0이면, B⊕M+0 = B⊕0+0 = B 따라서 A + B

4) M = 1이면, B⊕M+1 = B⊕1+1 = B'+1 = -B(2의 보수) 따라서 A - B

논리 마이크로 연산(Logic Microoperations)

1) 레지스터에 저장된 비트열에 대한 이진 연산으로서 각 비트를 독립된 이진 변수로 간주하고 연산을 수행한다.

2) 부울 대수에 있어서 OR, AND, 보수 연산과 구별하기 위하여 논리 마이크로 연산에서는 OR를 V로, AND를 ^로 표시한다.

예1) 제어변수 P가 1일때, P: R1 <- R1 ⊕ R2 즉, R1에는 1010 R2에는 1100이 있다고 가정한다면

P = 1 이후에 R1의 내용은 0110이 된다.

예2) P+Q = R1 <- R2+R3, R4 <- R5 V R6 *동시에 수행한다.

시프트 마이크로 연산(Shift Microoperations)

1) 데이터의 직렬 전송을 위하여 사용되며, 산술이나 논리 연산 및 다른 데이터 처리 동작과 연계하여 사용 가능

2) 레지스터의 내용은 왼쪽 및 오른쪽으로 시프트 될 수 있다.

3) 비트들이 시프트 될 때 첫 번째 플립플롭은 직렬 입력을 통하여 새로운 이진 정보를 받아들일 수 있다.

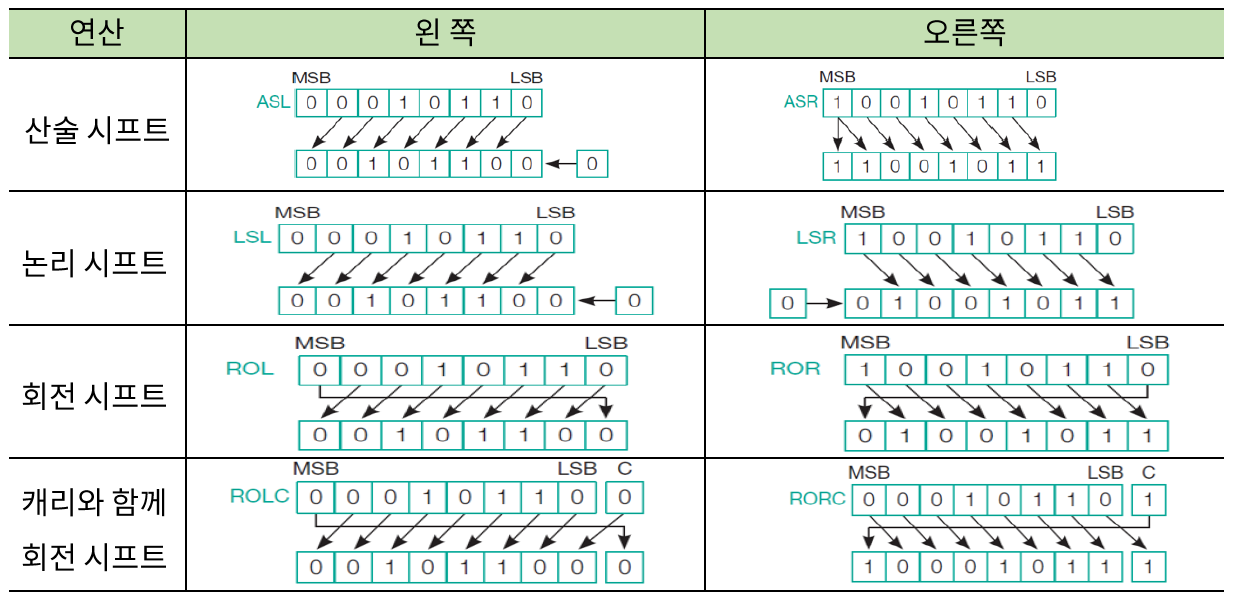

4) 입력되는 정보에 따라 논리, 순환, 산술 등의 세가지 종류로 나뉠 수 있다.

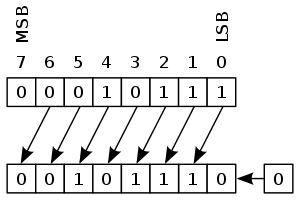

논리 시프트(Logical shift)

1) 논리 시프트에 의해 LSB나 MSB의 값들은 사라진다.

2) 직렬 입력으로 0이 전송되는 것으로, 기호는 shl(shift left), shr(shift right)라고 표시한다.

예1) R1 ← shl R1 = 왼쪽으로 시프트한다.

예2) R2 ← shr R2 = 오른쪽으로 시프트한다.

순환 시프트(Circular shift 또는 Rotate shift)

1) 시프트 레지스터의 직렬 출력을 직력 입력에 연결함으로써 원래 저장되어 있던 정보의 손실없이 비트들을 순환시키는 연산을 말한다.

2) 기호로는 왼쪽 및 오른쪽 순환 시프트를 각각 Circular shift left(cil/rol)와 Circular shift right(cir/ror)로 표시한다.

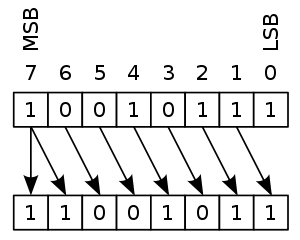

산술 시프트(Arithmetic shift)

1) 부호가 있는 이진수를 시프트하는 것이다.

2) 왼쪽 산술 시프트는 이진수에 2를 곱한 것이고, 오른쪽 산술 시프트는 2로 나눈 것이다.

3) 홀수에 대해서는 2로 나눔이 불가능하다.

4) 원래 Rn-1과 Rn-2가 다른 값이었다면 부호 비트의 반전이 발생하게 되고, 이것은 원래 레지스터의 값에 2를 곱하여 오버플로가 일어났음을 의미한다.

Vs = Rn-1⊕Rn-2

즉, Vs = 1일 때, 오버플로와 부호 반전이 일어나고 이 Vs값은 시프트 연산을 하기위한 클럭 펄스와 동시에 오버플로 플립플롭으로 전송된다.

총 정리

'컴퓨터 구조' 카테고리의 다른 글

| [컴퓨터 구조] 마이크로 프로그램을 이용한 제어 장치 (0) | 2022.05.21 |

|---|---|

| [컴퓨터 구조] 명령어 구조 및 실행 과정과 Hardwired 제어 장치 (0) | 2022.05.11 |

| [컴퓨터 구조] Register 전송 (0) | 2022.05.04 |

| [컴퓨터 구조] 소수 표현과 Error 검출 기법 (0) | 2022.04.13 |

| [컴퓨터 구조] Memory와 숫자 표현 (0) | 2022.04.11 |