*[Mano의 컴퓨터 시스템 구조 3판]의 공부할겸 요약한 내용입니다.

1. 레지스터 전송 언어(Register Transfer Language)

마이크로 연산(Micro-operation)

1) 레지스터에 저장된 데이터를 가지고 실행되는 동적을 마이크로 연산이라고 한다.

예) shift, clear, load, move, and, not, or, complement, increment, decrement 등

레지스터 전송 언어(Register Transfer Language)

1) 레지스터간의 마이크로 연산 전송을 보다 간단하고 명료하게 표시하기 위하여 사용하는 기호들을 레지스터 전송언어라고 한다.

2) 디지털 시스템의 설계를 편리하게 해준다.

2. 레지스터 전송(Register Transfer)

1) n비트 레지스터의 각 플립플롭들은 맨 오른쪽의 것을 0으로 하여 n-1까지 번호가 매겨져 있다.

2) 16비트 레지스터에 번호를 붙이는 방법은 두 부분으로 나눠진다.

2-1) 비트 0에서 7까지는 하위 바이트로 L(Low byte)라고 한다.

2-2) 비트 8에서 15까지는 상위 바이트로 H(High byte)라고 한다.

3) 레지스터들 사이의 정보 전송은 치환 연산자를 이용하여 다음과 같이 나타낸다.

R2 <- R1 (R1 레시스터의 n 출력이 R2 레지스터의 n 입력으로 연결된다.)

4) 제어함수: 0 또는 1의 값을 갖는 부울 변수로 보통 레지스터 전송이 정해진 제어 조건일 때만 발생하도록 if-then 문장을 사용한다.

if(P=1) then (R2 <- R1)

P: R2 <- R1

*P: R2 <- R1, R3 <- R5, R4 <- R1vR5 같은 경우 차례대로 진행되지 않고 동시에 진행된다.

3. 버스와 메모리 전송(Bus and Memory Transfers)

공통 버스(Common Bus)

1) 버스는 정보 등을 전송하기 위한 경로이다.

2) 공통 버스는 버스 구조를 단순화 하기 위해 제안된 방법이다.

3) 공통 버스를 구성하는 한 가지 방법으로 멀티플레서를 이용하는 것이 있다.

*각 레지스터에서 동일한 위치의 비트들은 모두 하나의 멀티플렉서에 연결되어 하나의 버스 라인을 형성하게 된다.

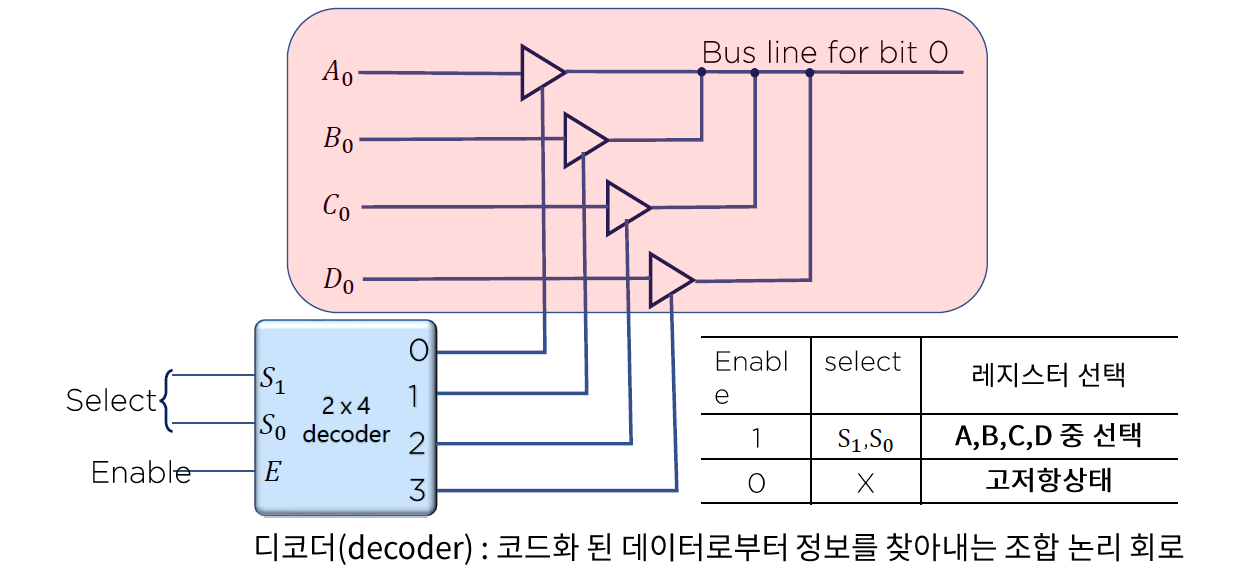

4) 버스 시스템은 멀티플렉서 대신 3-상태 게이트를 이용하여 구성할 수도 있다.

4-1) 제어 입력이 1일때는 보통의 버퍼같이 동작하여 그 출력은 입력과 동일한 값을 가진다.

4-2) 제어 입력이 0일때는 출력이 끊어지고 게이트는 고저항 상태가 된다.

4-3) 디코더를 이용하여 한 순간에 오직 하나의 3-상태 버퍼만이 활성화 되어 버스에 연결된다.

4-4) 나머지 버퍼는 모두 고저항 상태에 있도록 제어한다.

4-5) 디코더의 인에이블 입력이 0이면 4개 출력이 모두 0이므로 버스 라인은 고저항 상태가 된다.

4-6) 인에이블 입력이 0이면 디코더 입력값에 따라 3-상태 버퍼 중에서 하나가 활성화 된다.

'컴퓨터 구조' 카테고리의 다른 글

| [컴퓨터 구조] 명령어 구조 및 실행 과정과 Hardwired 제어 장치 (0) | 2022.05.11 |

|---|---|

| [컴퓨터 구조] 마이크로 연산 (0) | 2022.05.05 |

| [컴퓨터 구조] 소수 표현과 Error 검출 기법 (0) | 2022.04.13 |

| [컴퓨터 구조] Memory와 숫자 표현 (0) | 2022.04.11 |

| [컴퓨터 구조] Digital 부속품 요약 (0) | 2022.04.07 |