*[Mano의 컴퓨터 시스템 구조 3판]의 공부할겸 요약한 내용입니다.

조합 회로

- 입력과 출력을 가진 논리 게이트의 집합으로 출력의 값이 0과 1들로 조합된 함수이다.

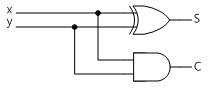

반가산기(Half Adder)

- 조합회로의 하나로, 두 비트를 더해서 캐리(Carry)와 몫을 구한다.

- 여기서 캐리(Carry)는 올림수를 일컫는다.

- 일반적으로 두 입력을 x, y로 표현하고 출력을 C(캐리), S(합)로 표현한다.

- Carry와 몫에 대해 각각의 K-map을 구한 후 여기서 각각의 부울함수를 추출하고, 이로부터 얻은 두개의 논리회로를 합쳐서 최종 하나의 회로를 얻는다.

- C는 입력 모두가 1일때만 1이고, S는 두 입력 중 하나의 입력만 1이여도 1이다. 따라서...

S = x'y + xy' = x ⊕ y

C= xy

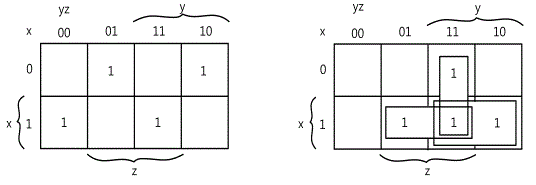

전가산기(Full-Adder)

- 비트 두개와 밑의 자리로부터 올라오는 캐리(Carry)까지 고려하여 비트 세 개를 가산하는 조합 회로이다.

- 3개의 입력(x, y, z)과 2개의 출력(C, S)으로 구성된다.

- Carry와 몫에 대해 각각의 K-map을 구한 후 여기서 각각의 부울함수를 추출하고, 이로부터 얻은 두개의 논리회로를 합쳐서 최종 하나의 회로를 얻는다.

- 3개의 비트를 더할 때 합은 0부터 3까지 나올 수 있고, 2와 3을 이진수로 표시한다.

S = x'y'z + x'yz' + xy'z' + xyz = x ⊕ y ⊕ z

C = xz + yz + xy = x'y + (xy + xy')z

을 통해 회로를 만들면...

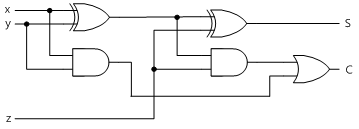

플립플롭(F/F: Flip-Flop)

- 순차회로에서 중요한 저장 요소이다.

- 한 비트의 정보를 저장할 수 있는 2진 셀(cell)이다.

- Register의 구성 요소이다.

- 정상 출력을 Q로 나타낸다.

- 두가지 출력 상태를 표현한다.

1) Q(t): 현재 상태의 출력 값

2) Q(t+1): 1Clock Cycle 후인 다음 상태의 출력 값

- 일반적으로 다름 4개의 플립플롭들이 존재한다.

1) SR F/F (Set/Reset Flip-Flop)

2) D F/F (Data Flip-Flop)

3) JK F/F (Jack/King Flip-Flop)

4) T F/F (Toggle Flip-Flop)

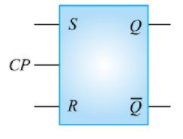

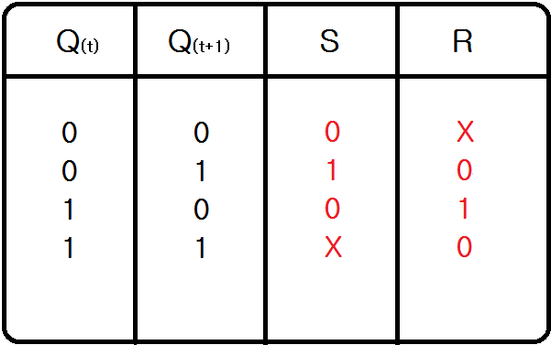

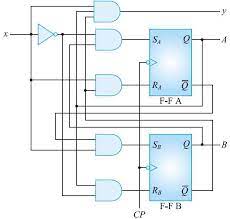

SR 플립플롭 (SR F/F)

- S(set), R(reset), C(clock)로 이름 붙여진 세 개의 입력과 하나의 출력 Q를 가지고 있다.

- S = 1이고 R = 0이면 출력 Q는 1이된다.

- S = 0이고 R = 1이면 출력 Q는 0이 된다.

- S와 R이 모두 0일 때 클럭 입력이 변하면 출력은 변화가 없다.

- S와 R이 모두 1일 때는 회로 내부의 시간 지연에 따라 출력값을 예상할 수 없다.

- Q(t)는 현재 상태의 출력값을, Q(t+1)은 클럭 신호가 변한 다음 상태의 출력값을 나타낸다.

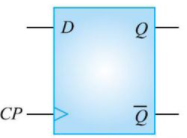

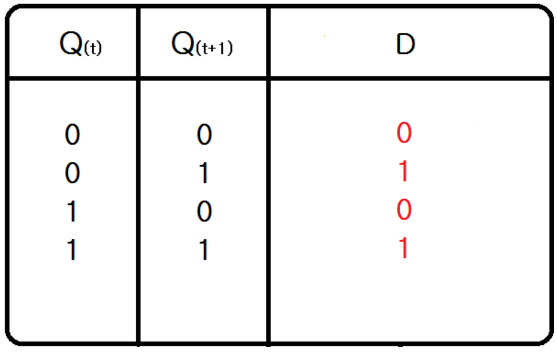

D 플립플롭 (D F/F)

- SR 플립플롭의 변형이다.

- D입력이 클럭 변이 (0에서 1) 동안 출력에 전달된다.

- D = 1일 때 출력은 1로 D = 0일 때 출력은 0으로 변한다.

- 입력과 다음 상태 사이의 관계는 Q(t+1) = D로 나타낼 수 있다.

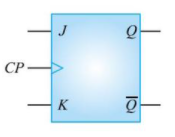

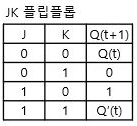

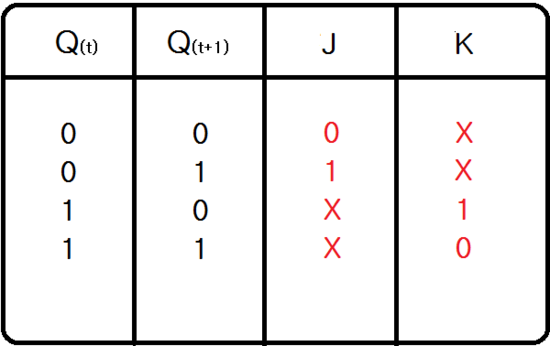

JK 플립플롭 (JK F/F)

- SR 플립플롭에서 S = R = 1 입력을 허용하지 않은 점을 보완한 플립플롭이다.

- 입력 J, K는 SR 플립플롭의 S,R에 해당한다.

- J = K = 1일 때 클럭 펄스는 플립플롭의 출력을 보수로 만든다. 즉, Q(t+1) = Q'(t)이 된다.

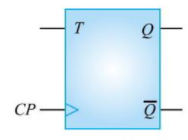

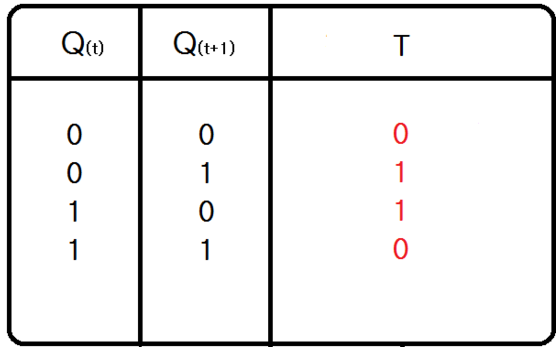

T 플립플롭 (T F/F)

- JK 플립플롭에서 입력 J와 K를 하나로 묶어 T라고 표시한다.

- T = 0인 경우 상태의 변화가 없고, T = 1인 경우 상태는 보수로 된다.

*모서리-번이형 플립플롭

- 상태 변경을 클럭 펄스의 변이 동안 동기화하는 것을 모서리-변이형 플립플롭이라고 한다.

여기표

- 플립플롭에서 현재 상태(Q(t))와 다음 상태(Q(t+1))를 알 때, 플립플롭에 어떤 입력을 넣어야 하는가를 표로 만든 것이다.

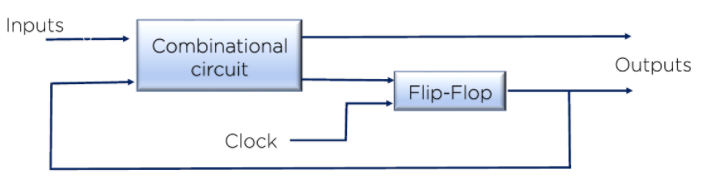

순차 회로(Sequential Circuits)

- 플립플롭과 게이트를 서로 연결한 것이다.

- 게이트로만 된 회로는 조합 회로이지만, 플립플롭이 포함될 때 순차 회로가 된다.

즉, 순차 회로 = 조합회로 + 플립플롭

'컴퓨터 구조' 카테고리의 다른 글

| [컴퓨터 구조] 소수 표현과 Error 검출 기법 (0) | 2022.04.13 |

|---|---|

| [컴퓨터 구조] Memory와 숫자 표현 (0) | 2022.04.11 |

| [컴퓨터 구조] Digital 부속품 요약 (0) | 2022.04.07 |

| [컴퓨터 구조] Karnaugh-map (0) | 2022.04.05 |

| [컴퓨터 구조] 디지털 시스템과 부울 대수 (0) | 2022.03.12 |